Video Processing with FPGA

Digitronix Nepal

4:14:49

Description

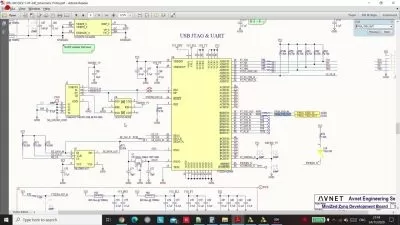

Implementing different Computer Vision Algorithm on Xilinx Zynq FPGA with VIVADO High Level Synthesis & SDK

What You'll Learn?

- Implement different Computer Vision algorithm for Video Processing

- Creating IP from the VIVADO High Level Synthesis

- IP integration and configuration with Xilinx VIVADO

- Xilinx SDK Application Development

- Migrating the OpenCV algorithm on XfOpenCV

- Simulating & Generating xfOpenCV codes in the VIVADO HLS

- Integrating TPG, VDMA and Writing application for this blocks

- Vitis HLS and OpenCV installation Session for 2020.2 or later

Who is this for?

What You Need to Know?

More details

DescriptionThis Course is on implementing different Video Processing algorithm on FPGA. We implement the algorithm on High Level Synthesis [HLS], simulate it with the image input, generate & export IPÂ from the HLS. The HLS IP is integrated with the necessary video processing pipeline [block design] and implemented on the FPGAÂ Device.

We have "Implemented Sobel Edge Detection, Dilation, Histogram Equalize, Fast Corner like algorithm" on HLS and then FPGA. For the debugging the algorithm on the FPGA, we have initialized the Test Pattern Generator [TPG] IP and Video DMA [VDMA] for processing the image streams on the DDR with the Processing System involvement.

After Completing this course you will be able to:

Utilized the HLS Video Processing Library and Implement as well as Simulate different OpenCV Algorithm on HLS

Integrating the HLS IP with Video Processing Pipeline with TPG and VDMAÂ and Implementing on the FPGA Device.

Implementing the XfOpenCV [SDSoC] Library on HLS for Computer Vision

Migrating the OpenCV algorithm into XfOpenCV

Who this course is for:

- Electrical Engineering Enthusiast

- Computer Science Enthusiast

- FPGA Design Professional

- Enthusiast of FPGA Design

This Course is on implementing different Video Processing algorithm on FPGA. We implement the algorithm on High Level Synthesis [HLS], simulate it with the image input, generate & export IPÂ from the HLS. The HLS IP is integrated with the necessary video processing pipeline [block design] and implemented on the FPGAÂ Device.

We have "Implemented Sobel Edge Detection, Dilation, Histogram Equalize, Fast Corner like algorithm" on HLS and then FPGA. For the debugging the algorithm on the FPGA, we have initialized the Test Pattern Generator [TPG] IP and Video DMA [VDMA] for processing the image streams on the DDR with the Processing System involvement.

After Completing this course you will be able to:

Utilized the HLS Video Processing Library and Implement as well as Simulate different OpenCV Algorithm on HLS

Integrating the HLS IP with Video Processing Pipeline with TPG and VDMAÂ and Implementing on the FPGA Device.

Implementing the XfOpenCV [SDSoC] Library on HLS for Computer Vision

Migrating the OpenCV algorithm into XfOpenCV

Who this course is for:

- Electrical Engineering Enthusiast

- Computer Science Enthusiast

- FPGA Design Professional

- Enthusiast of FPGA Design

User Reviews

Rating

Digitronix Nepal

Instructor's Courses

Udemy

View courses Udemy- language english

- Training sessions 23

- duration 4:14:49

- Release Date 2024/04/20