RISC-V Interrupts & Platform Level Interrupt Controller

Benix Samuel Vincent Theogaraj

2:05:07

Description

Write RISC-V assembly code to configure GPIO, PLIC and Core CSRs to generate GPIO interrupt and blink blue LED on board

What You'll Learn?

- Understand privilege levels, traps and control and status registers in RISC-V

- Platform Level Interrupt Controller Specification for RISC-V

- Sample implementation of PLIC module on RISC-V based FE310 SoC

- Writing assembly code, compiling, linking with GNU tools and debugging with OpenOCD and GDB

- Demonstration of interrupt generation & handling in RISC-V assembly

Who is this for?

What You Need to Know?

More details

DescriptionInterrupts in RISC-V are governed by standards and specification. Each RISC-V core's interrupt generation and handling process should be compliant to the specification.

This course discusses the following:

a. Privilege Levels in RISC-V

b. Traps in RISC-V

c. Platform Level Interrupt Controller (PLIC) Specification

d. Compares PLICÂ Implementation on FE310 SoC to Spec

e. Control and Status Registers (CSRs)

f. Instructions to read and write CSRs in RISC-V

g. Configuring GPIOÂ peripheral in FE310 SoC

h. Configuring PLICÂ to allow GPIOÂ interrupt

i. Configure MIE & MSTATUS CSRs on the core to enable machine mode interrupts and machine mode external interrupts

j. Installation of GNUÂ tools (compilers, OpenOCD)

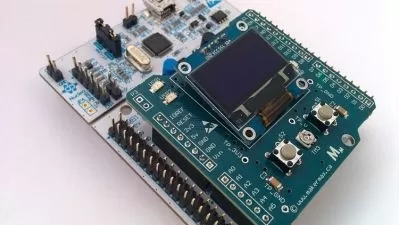

k. Test application in assembly to blink blue LEDÂ on Hifive1-Rev B board.

Students who enrol would be taken through a journey starting from basics of what are interrupts, exceptions and traps in RISC-V, followed by PLIC standard discussing the parameters, how to configure those parameters on PLICÂ to generate interrupt and claiming and completing the interrupt handling process and finally on writing an test application to blink LED.

The major exercise and focus on this course is on writing RISC-V assembly code, assembling &Â linking with GNUÂ tools, generating ELF, and programming it on Hifive1-RevB board to blink blue LED on board.

Who this course is for:

- Embedded system developers and RISC-V enthusiasts

Interrupts in RISC-V are governed by standards and specification. Each RISC-V core's interrupt generation and handling process should be compliant to the specification.

This course discusses the following:

a. Privilege Levels in RISC-V

b. Traps in RISC-V

c. Platform Level Interrupt Controller (PLIC) Specification

d. Compares PLICÂ Implementation on FE310 SoC to Spec

e. Control and Status Registers (CSRs)

f. Instructions to read and write CSRs in RISC-V

g. Configuring GPIOÂ peripheral in FE310 SoC

h. Configuring PLICÂ to allow GPIOÂ interrupt

i. Configure MIE & MSTATUS CSRs on the core to enable machine mode interrupts and machine mode external interrupts

j. Installation of GNUÂ tools (compilers, OpenOCD)

k. Test application in assembly to blink blue LEDÂ on Hifive1-Rev B board.

Students who enrol would be taken through a journey starting from basics of what are interrupts, exceptions and traps in RISC-V, followed by PLIC standard discussing the parameters, how to configure those parameters on PLICÂ to generate interrupt and claiming and completing the interrupt handling process and finally on writing an test application to blink LED.

The major exercise and focus on this course is on writing RISC-V assembly code, assembling &Â linking with GNUÂ tools, generating ELF, and programming it on Hifive1-RevB board to blink blue LED on board.

Who this course is for:

- Embedded system developers and RISC-V enthusiasts

User Reviews

Rating

Benix Samuel Vincent Theogaraj

Instructor's Courses

Udemy

View courses Udemy- language english

- Training sessions 15

- duration 2:05:07

- Release Date 2024/05/28