Introduction to VHDL for FPGA and ASIC design

Focused View

Scott Dickson

7:08:20

4 View

1 - Basic VHDL.html

1 - Why VHDL.mp4

23:48

2 - First VHDL design.mp4

32:04

3 - Acquiring a VHDL simulator.mp4

01:26

4 - Download and install Altera Modelsim.mp4

01:39

4 - lab4byinstructor.zip

5 - Download and install Xilinx Vivado Simulator.mp4

01:38

6 - Vivado Simulator Demonstration.mp4

06:20

7 - Modelsim Altera Quartus Demonstration.mp4

08:03

8 - Alternate Lab 1 Solution using Vivado.mp4

06:10

2 - Concurrent and Sequential VHDL Quiz.html

9 - The VHDL Process.mp4

19:39

10 - Concurrent and Sequential Statements.mp4

26:53

11 - VHDL Hierarchy.mp4

21:53

12 - Testbench Demo with Vivado.mp4

10:07

13 - Testbench Demo with Modesim.mp4

06:07

3 - RTL.html

14 - Understanding the FlipFlop.mp4

25:32

15 - Synchronous Design Methodolgy.mp4

21:06

16 - RTL Styles.mp4

22:33

4 - VHDL Types.html

17 - Multivalue logic stdlogic.mp4

18:26

18 - Logic Arrays and Variables.mp4

24:15

19 - State Machines.mp4

33:50

5 - VHDL Operators.html

20 - VHDL logical and relational operators.mp4

21:35

21 - Math Operators.mp4

33:03

22 - Functions Procedures and Packages.mp4

18:08

6 - Verification.html

23 - Verification.mp4

12:43

24 - Self Checking Testbenches.mp4

31:22

Description

From VHDL basics to sophisticated testbench coding

What You'll Learn?

- Practical FPGA and ASIC RTL design using VHDL

Who is this for?

What You Need to Know?

More details

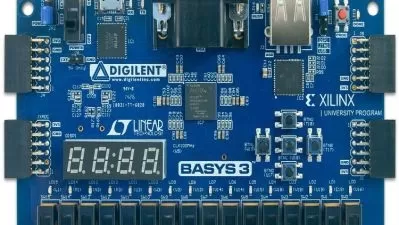

DescriptionTwelve lectures, starting from the basics of VHDL, including the entity, architecture, and process. Explanations of the difference in sequential and concurrent VHDL. Discussions of good synchronous design methodology. Demonstrations on how to use the Altera Modelsim and Xilinx Vivado simulators. Six lab projects for hands-on experience, with the instructor showing how he would have done each lab.

Who this course is for:

- Beginner FPGA or ASIC designer

Twelve lectures, starting from the basics of VHDL, including the entity, architecture, and process. Explanations of the difference in sequential and concurrent VHDL. Discussions of good synchronous design methodology. Demonstrations on how to use the Altera Modelsim and Xilinx Vivado simulators. Six lab projects for hands-on experience, with the instructor showing how he would have done each lab.

Who this course is for:

- Beginner FPGA or ASIC designer

User Reviews

Rating

average 0

Focused display

Scott Dickson

Instructor's CoursesTwenty five years of experience in designing FPGAs and ASICs for the commercial and aerospace markets. Instructor for many years at California State University. Lecturer and instructor for major companies including Boeing, Rockwell, Intel, Xilinx, and AMD. FPGA designs in aerospace, communications, image processing, and automation. Popular lecturer for development seminars and company learning events.

Udemy

View courses UdemyStudents take courses primarily to improve job-related skills.Some courses generate credit toward technical certification. Udemy has made a special effort to attract corporate trainers seeking to create coursework for employees of their company.

- language english

- Training sessions 24

- duration 7:08:20

- English subtitles has

- Release Date 2024/04/13